Na coluna anterior da série vimos como é possível transmitir um dado entre dois componentes através de um conjunto de condutores paralelos (barramento). Usamos como exemplo um barramento de oito linhas de dados, capaz de transportar valores expressos em um byte (oito bits transportados simultaneamente nas oito linhas) entre UCP e MP, parte do chamado “barramento frontal” (as demais partes do barramento frontal são as linhas de endereços e as de controle; veja a coluna “Placas-mãe e memória principal”).

Vimos ainda que o valor é transportado aplicando-se tensões elétricas em uma das extremidades de cada linha e lendo estas tensões na extremidade oposta usando como referência para o momento exato em que as tensões devem ser aplicadas (e lidas) o chamado “sinal de clock”, constituído por um pulso de tensão aplicado em intervalos regulares a uma linha do barramento de controle designada especificamente para este fim, ou a linha CLK. E vimos que este procedimento é a essência da chamada “lógica temporizada”.

Porém tudo isso refere-se à forma física pela qual o valor é transportado. E o que mais nos interessa são os aspectos lógicos da questão. Aspectos que tentaremos abordar agora examinando o procedimento adotado para efetuar a escrita (armazenamento de um número em uma posição de memória) ou leitura (recuperação de um número previamente escrito em uma posição de memória) na MP.

Mas, antes de prosseguirmos, uma observação. Quem acompanha a evolução do hardware usado nos computadores modernos talvez tenha a impressão que os novos módulos de memória “DDR” (de “Double Data Rate”, ou taxa de dados dupla) desafiam a lógica. Ou pelo menos a lógica temporizada, já que são capazes de transferir mais de um conjunto de bits (dois conjuntos, no caso dos módulos DDR simples, quatro no caso dos DDR2) em cada ciclo de clock. No ponto em que estamos de nossa jornada em busca do entendimento das entranhas do computador nos faltam conhecimentos para entender como isso pode ser feito. Deixemos então esse tipo de detalhe para mais adiante quando, depois de destrincharmos a CPU, começaremos a discutir a memória. Por enquanto vamos usar como exemplo um tipo de memória que praticamente caiu em desuso, as velhas memórias FPM (de Fast Page Mode; se você quiser saber um pouco mais sobre elas leia a excelente série de colunas do Mestre Abel Alves sobre memórias). São memórias antigas, é verdade, porém mais simples. E justamente por isso será mais fácil entendermos como funcionam. Como a lógica das operações de leitura e escrita nas velhas memórias é essencialmente a mesma usada nas modernas (o que varia é apenas o ritmo em que as operações se sucedem), adotaremos como exemplo as mais simples apenas para facilitar o entendimento. Então, já alertados para o fato de que o procedimento abaixo descrito aplica-se às memórias tipo FPM, vamos adiante.

Para ler ou escrever algo na MP são necessários três parâmetros: o endereço da posição de memória na qual a operação será efetuada, um sinal de controle indicando o tipo da operação (leitura ou escrita) e, no caso da escrita, o valor a ser escrito. Tudo isso, naturalmente, sincronizado com os sinais de “clock”.

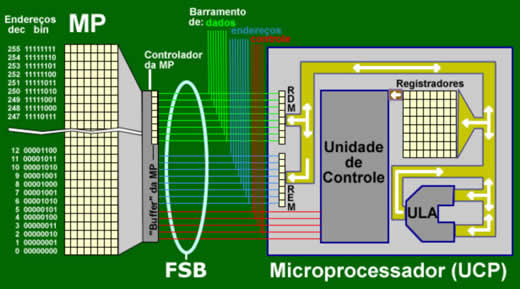

Vamos entendermos as operações de leitura e escrita na memória vamos recorrer à Figura 1, a parte do esquema da placa-mãe que nos interessa no momento, mostrando a UCP com seus componentes internos, a MP com seu controlador e o trecho do barramento entre UCP e MP denominado barramento frontal ou FSB (de Front Side Bus; note que, conforme mostra a figura, o barramento frontal é subdividido nos barramentos de dados, endereços e controle).

|

| Figura 1: UCP, MP e FSB |

Vamos começar pela operação de escrita na MP. Como se percebe da Figura 1, a única forma da UCP se comunicar com os barramentos de dados e endereços é através dos registradores RDM e REM. Portanto, para efetuar uma operação de escrita na memória, os números correspondentes ao dado a ser escrito e ao endereço da posição da memória que irá armazená-lo deverão ter sido previamente escritos no RDM e REM, respectivamente. Por enquanto vamos ignorar como isso é feito: é tarefa interna da UCP e por ora basta saber que para iniciar o procedimento de escrita de um número em uma posição de memória é preciso que tanto o número a ser escrito quanto o endereço da posição de memória que irá recebê-lo estejam presentes respectivamente no RDM e REM. Imaginemos que o número a ser escrito seja 10101010 (170 em decimal) e o endereço onde ele deverá ser escrito seja 11111010 (250 em decimal).

Neste ponto inicia-se o procedimento de escrita. Os circuitos internos da Unidade de Controle da UCP, de onde partem as linhas do barramento de controle mostradas em vermelho nas figuras, aguardam o próximo pulso de clock (lembre da lógica temporizada discutida na coluna anterior) e assim que ele é emitido aplicam um sinal, também sob a forma de um pulso de tensão elétrica, na linha do barramento de controle correspondente à escrita na memória (Memory Write).

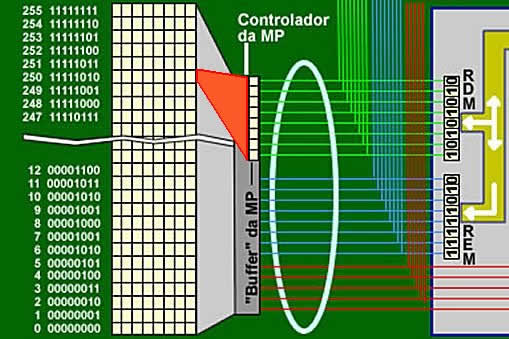

Quando o controlador da memória constata que há um pulso na linha “Memory write”, ainda no mesmo ciclo de “clock”, prepara-se para a operação de escrita lendo o conteúdo do REM (ou seja, o endereço onde o dado será escrito) e “apontando” seus circuitos internos para este endereço. A situação será similar à representada pela Figura 2. Observe, na figura, o conteúdo dos registradores RDM e REM e note que o buffer da MP, uma posição de memória auxiliar contida no interior do controlador da memória, embora vazio, “aponta” para o endereço 11111010. E lembre que tudo isto ocorreu em um único ciclo do barramento, ou seja, após um único pulso de clock.

|

| Figura 2: Situação após o controlador da MP receber o sinal “Memory Write”. |

O controlador da memória agora “sabe” que no próximo ciclo ele deverá realizar uma operação de escrita na MP (graças ao sinal “Memory write”) e “sabe” em que posição de memória o valor deverá ser escrito (pois já “apontou” seus circuitos internos para ele). Agora é só aguardar o próximo pulso de clock.

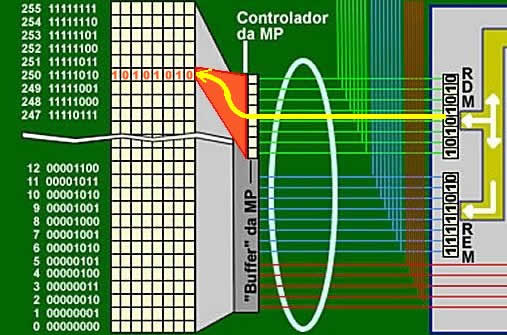

No momento em que ele é disparado o controlador da MP lê o conteúdo do RDM ou seja, ausculta suas extremidades das linhas do barramento de dados para verificar quais estão energizadas (bit “um”) e quais não estão (bit “zero”), transpõe esses bits para o buffer da MP e daí os transfere para o endereço lido anteriormente no REM. O resultado final é o exibido na Figura 3: o valor binário 10101010 escrito no endereço 11111010. A operação de escrita na memória foi finalizada com sucesso.

|

| Figura 2: Situação após encerrada a operação de escrita na MP |

No caso da operação de leitura, as coisas se passam de forma semelhante. Primeiro, os circuitos de controle escrevem no REM o endereço de onde o dado será lido. No momento em que é disparado o próximo pulso na linha de clock, a unidade de controle dispara um pulso simultâneo em uma outra linha do barramento de controle, a linha denominada “Memory read” que informa ao controlador da MP que a próxima operação será de leitura.

No momento em que o circuito de controle da memória detecta o sinal na linha “Memory read” ele toma conhecimento que deverá fornecer à UCP um dado armazenado em um certo endereço de memória, aquele que foi previamente escrito no REM. E, durante o mesmo ciclo, lê o conteúdo do REM e “aponta” seus circuitos internos para o endereço correspondente.

Agora é só aguardar o próximo pulso na linha de “clock”. No momento em que ele é disparado o controlador da MP lê o conteúdo do endereço para o qual já está “apontando”, o copia no buffer da MP e o transfere imediatamente para o RDM, onde a UCP irá buscá-lo para fazer bom uso dele. E com isso se encerra a operação de leitura da MP.

Como se vê, é tudo muito simples.

Para finalizar, uma observação interessante: o mecanismo acima descrito permite entender porque a UCP não consegue executar instruções que impliquem operações binárias (com dois operandos) nas quais ambos os operandos estão armazenados na memória principal (por exemplo: somar dois números, cada um armazenado em uma posição da MP). A razão é que a UCP somente consegue “enxergar” o conteúdo de uma posição de memória de cada vez (aquele cujo endereço está no RDM) e para realizar uma operação binária a UCP deve alimentar a ULA com ambos os operandos simultaneamente. Assim, é possível somar com uma única instrução, por exemplo, o valor contido no Acumulador com o de uma determinada posição de memória (cujo valor é lido e copiado no RDM), já que a ULA pode ser alimentada simultaneamente com ambos os valores, posto que estão contidos em dois registradores (Acumulador e RDM). Mas não é possível fazer o mesmo com dois valores armazenados na memória principal (é claro que esta operação pode ser viabilizada em dois passos, cada um correspondendo a uma instrução: no primeiro, um dado e lido da memória e copiado no acumulador, no segundo este valor é somado com o conteúdo da segunda posição de memória, copiado no RDM; o que é impossível é realizar esta operação com uma única instrução em linguagem de máquina).

Agora que sabemos como os dados são movimentados entre MP e UCP estamos prontos para entender o “ciclo de busca e execução”, aquele que permite à UCP ler e executar instruções sucessivamente. Ou seja: como funcionam os programas.

Na próxima coluna, naturalmente...

B.

Piropo